Introduction:

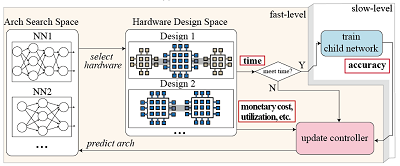

Figure: Illustration of co-exploring neural architectures and hardware designs

Figure: Illustration of co-exploring neural architectures and hardware designs

As the increasing number of applications (ranging from mobile and connected home to security, surveillance and automotive) that combine edge computing and machine learning, implementing neural networks on edge devices become ever more important; however, with limited hardware resources on the edge devices and the restricted timing specification, neural networks that attain state-of-the-art accuracy will not fit. We establish that in order to achieve the highest accuracy and hardware efficiency on the edge, it is best to co-explore hardware design and neural architecture (the above figure), rather than taking state-of-the-art approaches that either explore neural architecture only assuming fixed hardware, or explore hardware design only assuming fixed neural architecture. The proposed co-exploration framework opens up the hardware design freedom, which can significantly push forward the Pareto frontiers between hardware efficiency and test accuracy, and we can obtain much better design trade-offs than the existing approaches. Our contribution can be seen as an analogy to the concept of hardware-software co-design, which has prevailed due to its superior.

We aim to develop a full-stack tools to support co-exploration of neural architecture and hardware design from (1) optimization of fixed neural network on FPGAs; (2) FPGA-implementation aware NAS; (3) co-explore neural architectures on multiple FPGAs; (4) co-explore neural architecture on network-on-chip-based scalable hardware.

Members:

Weiwen Jiang

Xinyi Zhang (Ph.D. candidate @ PITT)

Qing Lu (Ph.D. candidate @ ND)

Lei Yang (Postdoc @ GWU)

Publications:

1.

Dancing along Battery: Enabling Transformer with Run-time Reconfigurability on Mobile Devices [arXiv avaiable soon]

Y. Song, W. Jiang, B. Li, P. Qi, Q. Zhuge, E. H.-M. Sha, S. Dasgupta, Y. Shi, and C. Ding

Accepted by Design Automation Conference (DAC), 2021

2.

A Co-Design Framework of Neural Networks and Quantum Circuits Towards Quantum Advantage

W. Jiang, J. Xiong, and Y. Shi

3.

When Machine Learning Meets Quantum Computers: A Case Study

W. Jiang, J. Xiong, and Y. Shi

in Proc. of Asia and South Pacific Design Automation Conference (ASP-DAC), (invited paper) [arXiv];

4.

Achieving Full Parallelism in LSTM via a Unified Accelerator Design

X. Zhang, W. Jiang, J. Hu

IEEE International Conference on Computer Design (ICCD2020@Online), Oct. 2020.

(acceptance rate 62/221=28.1%)

5.

Hardware Design and the Competency Awareness of a Neural Network

Y. Ding, W. Jiang, Q. Lou, J. Liu, J. Xiong, X. Sharon Hu, X. Xu, and Y. Shi,

Nature Electronics, Aug. 2020 (in print)

6.

Standing on the Shoulders of Giants: Hardware and Neural Architecture Co-Search with Hot Start [arXiv]

W. Jiang, L. Yang, S. Dasgupta, J. Hu and Y. Shi

International Conference on Hardware/Software Co-design and System Synthesis CODE+ISSS) in ESWEEK'20

(acceptance rate 94/375=25.1%)

also appears at IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), Virtaul Conference, Oct. 2020.

7.

Device-Circuit-Architecture Co-Exploration for Computing-in-Memory Neural Accelerators [arXiv]

W. Jiang, Q. Lou, Z. Yan, L. Yang, J. Hu, X. S. Hu and Y. Shi

IEEE Transactions on Computers (TC), Accepted, 2020.

8.

Hardware/Software Co-Exploration of Neural Architectures [arXiv]

W. Jiang, L. Yang, E. H.-M. Sha, Q. Zhuge, S. Gu, S. Dasgupta, Y. Shi and J. Hu

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), Accepted, 2020.

9.

Co-Exploration of Neural Architectures and Heterogeneous ASIC Accelerator Designs Targeting Multiple Tasks [arXiv]

L. Yang, Z. Yan, M. Li, H. Kwon, L. Lai, T. Krishana, V. Chandra, W. Jiang, and Y. Shi

Design Automation Conference (DAC), 2020.

(acceptance rate 228/992=23.0%)

10.

NASS: Optimizing Secure Inference via Neural Architecture Search [arXiv]

B. Song, W. Jiang, Q. Lu, Y. Shi and T. Sato

Proc. European Conference on Artificial Intelligence (ECAI), Santiago de Compostela, June. 2020.

(acceptance rate 365/1363=26.8%)

11.

Co-Exploring Neural Architecture and Network-on-Chip Design for Real-Time Artificial Intelligence (BEST PAPER NOMINATION)

L. Yang*, W. Jiang*, W. Liu, E. H.-M. Sha, Y. Shi and J. Hu

Proc. Asia and South Pacific Design Automation Conference (ASP-DAC), Beijing, Jan. 2020.

(acceptance rate 86/263=32.6%; * equal contribution)

12.

Achieving Super-Linear Speedup across Multi-FPGA for Real-Time DNN Inference [arXiv] (BEST PAPER NOMINATION)

W. Jiang, E. H.-M. Sha, X. Zhang, L. Yang, Q. Zhuge, Y. Shi and J. Hu

International Conference on Hardware/Software Co-design and System Synthesis CODE+ISSS) in ESWEEK'19

(acceptance rate 66/243=27.2%)

also appears at ACM Transactions on Embedded Computing Systems (TECS), NYC, New York, USA, Oct. 2019.

13.

Integrating Memristors and CMOS for Better AI

W. Jiang, B. Xie, C-C Liu and Y. Shi,

Nature Electronics (News and Views), Sep. 2019

14.

When Neural Architecture Search Meets Hardware Implementation: from Hardware Awareness to Co-Design (Invited paper)

X. Zhang, W. Jiang, Y. Shi and J. Hu,

Proc. IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Miami, Florida, USA, Aug. 2019.

15.

On Neural Architecture Search for Resource-Constrained Hardware Platforms (Invited paper)

Q. Lu, W. Jiang, X. Xiao, J. Hu and Y. Shi,

Proc. IEEE/ACM International Conference On Computer-Aided Design (ICCAD), Westminster, CO, 2019.

16.

Accuracy vs. Efficiency: Achieving Both through FPGA-Implementation Aware Neural Architecture Search [arXiv]

(BEST PAPER NOMINATION)

W. Jiang, X. Zhang, E. H.-M. Sha, L. Yang, Q. Zhuge, Y. Shi, and J. Hu

Design Automation Conference (DAC), 2019.

(acceptance rate 204/815=25%)

17.

Heterogeneous FPGA-based Cost-Optimal Design for Timing-Constrained CNNs

W. Jiang, E. H.-M. Sha, Q. Zhuge, L. Yang, X. Chen, and J. Hu

International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES) in ESWEEK'18

(acceptance rate 67/270=24.8%)

also appear at IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), Torino, Italy, Oct. 2018.

Hornors: